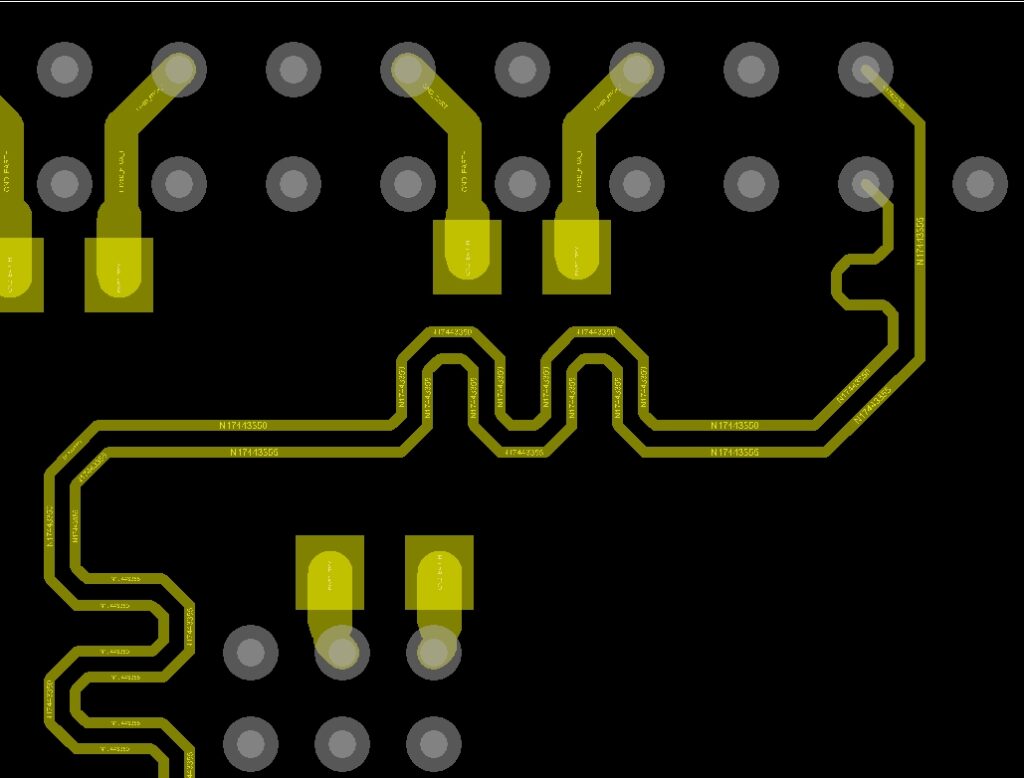

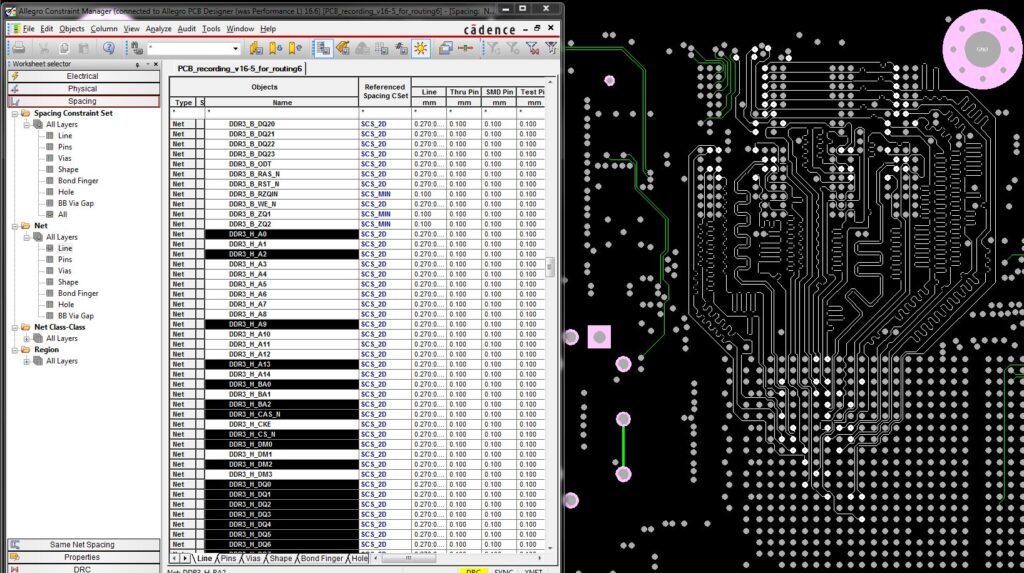

Same net spacing

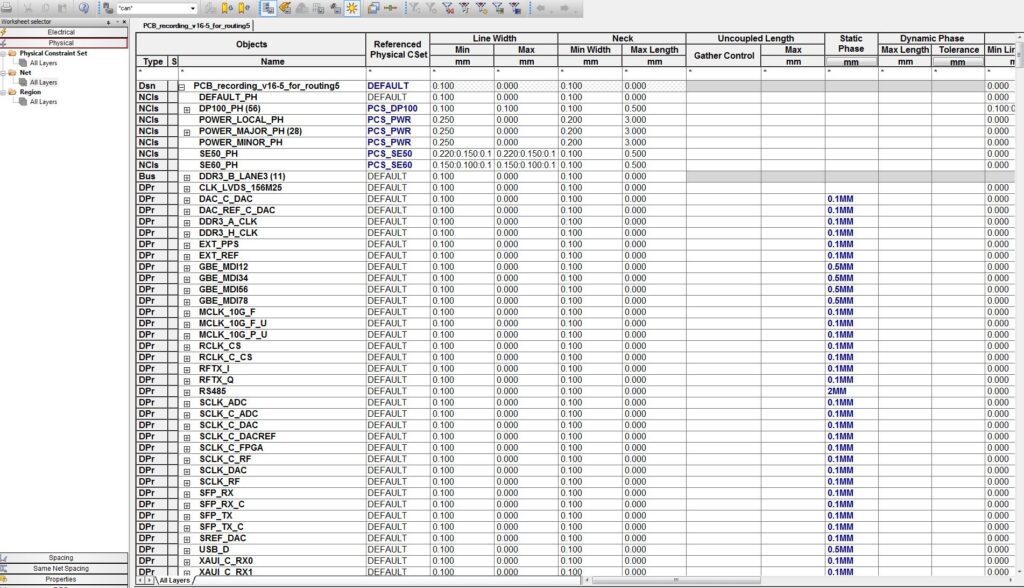

Length matching and tuning can result in “serpentine” routing where extra length is added to a trace; in these cases, signal integrity concerns may require that the looping patterns within the same net are subject to a specific minimum spacing – typically this is 2x to 4x the vertical distance from the layer to an adjacent reference (ground or power) plane

Stubs & Constraint regions

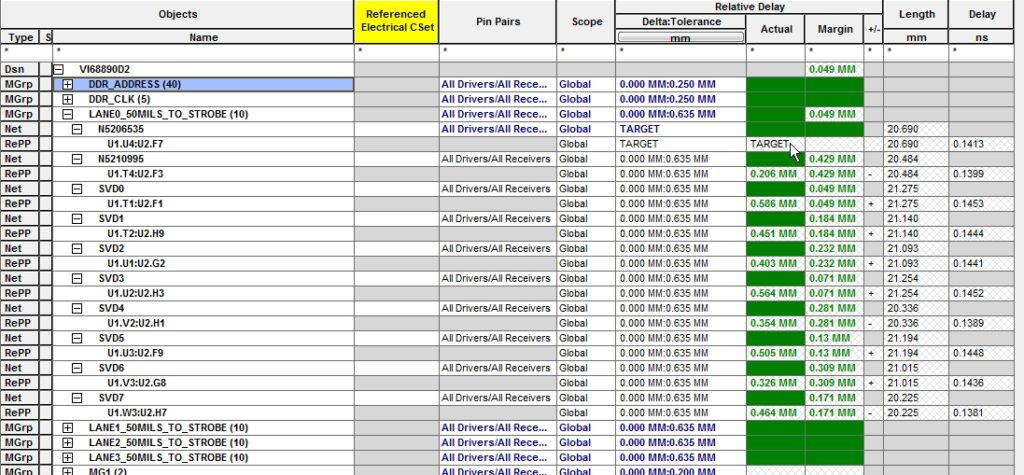

Stubs: Typically used in combination with scheduling, stub lengths can be constrained as required to meet signal integrity requirements

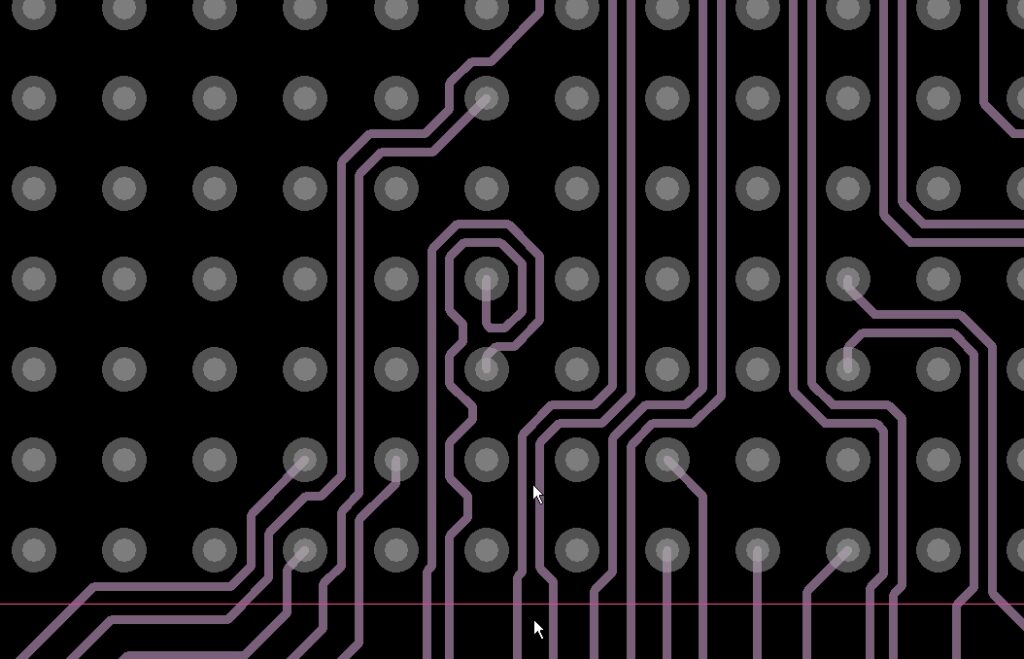

Constraint regions: specific areas can be specified within which different physical and spacing constraints may be applied, for example in the escape region of a BGA